【導讀】設計人員選擇具有優(yōu)秀調試能力的FPGA器件,可以縮短開發(fā)周期并降低成本,同時顯著加快上市速度。FPGA和SoC設計人員要克服許多挑戰(zhàn),才可以把產品投入生產。

一般說來,他們首先要為自己的設計評估合適器件;然后,使用硬件描述語言(HDL)設計,布局布線器件,最后,在投入生產之前,還要對整個FPGA進行調試。

對于許多設計,特別是工業(yè)和嵌入式市場的設計來說,可以選擇的FPGA實在多不勝數(shù)。在大多數(shù)情況下,決定選擇哪家FPGA供應商取決于其相關的軟件開發(fā)經(jīng)驗。雖然軟件開發(fā)經(jīng)驗也應該是考慮因素,但是,更重要的因素應該是調試能力及為加速生產提供的支持。目前,阿爾特拉(Altera)、萊迪思(Lattice)、美高森美(Microsemi)和賽靈思(Xilinx)等供應商都提供許多FPGA調試工具,但是,設計人員對未來的FPGA設計策略進行評估時,應該考慮采用一種更智能的調試工具。

基礎調試 – 邏輯分析儀

每個主要的FPGA供應商都提供邏輯分析儀作為調試工具。這是一種利用內部FPGA邏輯單元和嵌入式塊存儲器來實施功能的技術。設計人員可以規(guī)定監(jiān)測哪種信號,并設置觸發(fā)器來告訴邏輯分析儀何時開始采集數(shù)據(jù)。邏輯分析儀設置好后,設計人員必須重新按順序運行綜合和布局布線,將功能納入到設計中。設計重新編譯和重新編程后,設計人員便可以開始觀察邏輯分析儀采集的邏輯信號。

需要注意的是,由于這些信號需要采樣,它們采集的并非數(shù)據(jù)的實時性能。邏輯分析儀只能以允許其采集數(shù)據(jù)的速度運行,并將數(shù)據(jù)保存在內部存儲器內。由于設計必須重新編譯以插入邏輯分析儀,因此,這一過程實際上可能消除正在尋找的漏洞。雖然這看起來似乎不錯,但是,不了解原問題是什么,意味著后面再執(zhí)行合成和布局布線操作時,問題可能會再次產生和重新出現(xiàn)。

盡管如此,設計人員能夠根據(jù)觸發(fā)條件來查看信號狀態(tài),這樣做確實可以幫助調試設計問題。采用邏輯分析儀是一個不斷迭代的過程。設計人員查找發(fā)生的問題,進行更新,然后對設計進行重新編譯,再審查新的結果,然后重復這個過程,直到發(fā)現(xiàn)漏洞。每個迭代和處理每個具體漏洞所需的時間都不同,由于邏輯分析儀的采樣速度,因此不一定可以找到所有問題。

下一代調試工具

由于邏輯分析儀在調試方面的限制,業(yè)界設計了新一代調試工具,以加快FPGA和板的驗證。有些EDA供應商在綜合工具內集成了邏輯分析儀功能,縮短了漏洞查找迭代的時間,能夠查看設計和使觸發(fā)設置更簡單。設計人員還可以更改設計,使其自動映射回到寄存器傳送級(RTL)代碼。為了節(jié)約內部FPGA資源,有些EDA工具可以采集多組信號,并將它們多路復用。在調試過程初期,我們不知道問題的實際源頭時,這樣做很有幫助。新思科技(Synopsys)在其identify邏輯分析儀和Synplify綜合工具中已經(jīng)實施了這些特點。盡管他們?yōu)檎{試過程提供了這些改進,但是,這些方法因需要重新編譯,因而影響原始設計和減慢信號采集,所以受到限制。

實際上,對工程師有幫助的,除了邏輯分析儀,還有示波器。這種功能允許實時顯示器件內部信號。用探頭實時探測FPGA內的節(jié)點,強制賦予內部信號不同值,觀察對設計的即時影響,也是十分理想的。此外,探測內部存儲器的能力以及SERDES收發(fā)器探測點也是非常有用的。如果能夠提供所有這些能力而不影響FPGA設計,將顯著簡化調試過程。

這種方法的一個實例是美高森美Libero SoC軟件中的SmartDebug工具箱,該工具箱與公司的SmartFusion2、IGLOO2和RTG4 FPGA一起使用。這個工具箱使設計人員能夠調試FPGA結構、存儲塊和SERDES,就好象它們正在使用示波器一樣。采用這種智能調試,可以利用內置在FPGA結構中的專用探測點,顯著加快和簡化調試過程。不需要對設計進行重新編譯就可以選擇不同的探測點。增強的調試特點可訪問任何邏輯元件,使設計人員能夠實時檢查輸入和輸出狀態(tài),不影響用戶的FPGA設計。這些特點包括:

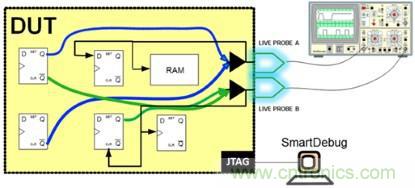

-現(xiàn)場探頭:允許采用兩個專用探頭,經(jīng)配置用于觀察邏輯元件中任何輸入或輸出的探測點(圖1)。然后,探頭數(shù)據(jù)可發(fā)送到示波器或甚至重新引導回到FPGA結構,驅動內部邏輯分析儀。這些探測點是實時動態(tài)的。探測點可以通過軟件在運行中更改,不需要把FPGA重新編譯或重新編程。

-有源探頭:這種特點允許動態(tài)異步讀取或寫入觸發(fā)器或探測點。這種能力使用戶能夠快速從內部觀察邏輯輸出或通過寫入探測點,快速實驗邏輯將受到怎樣的影響??蓪⑷魏螖?shù)量的信號強制賦予到規(guī)定值,正如現(xiàn)場探頭一樣,不需要把FPGA重新編譯或重新編程。

-探頭插入:這用于在設計中插入其它探頭,將信號輸出到FPGA封裝引腳,以對設計進行評估和調試。這種特點確實需要增加布局布線,從而在I/O增加信號,但并不一定需要完整的重新編譯。

圖1 現(xiàn)場探頭使用實例(來源:美高森美)

FPGA設計人員把30%或更多的時間通?;ㄔ谡{試上。根據(jù)項目的規(guī)模和狀態(tài),甚至需要更多的調試時間。由于調試涉及許多迭代周期,可觀察性和可控性有限,經(jīng)常要重新運行布局布線,時序收斂和重新編程,因此調試是非常痛苦的工作。與僅使用傳統(tǒng)插入邏輯分析儀相比,智能調試工具使得工程師能夠更快地對他們的FPGA設計進行驗證。這些工具使得設計人員在整個設計中可以實時觀察信號和控制信號狀態(tài),顯著提高了調試速度。

最近,據(jù)一名客戶報告,他們采用內部邏輯分析儀花了一周時間來試圖調試一個問題。但在采用智能調試工具代替后,工程師僅僅在兩個小時內就找出了問題。最終追蹤到,這個問題來自與工程師采用邏輯分析儀時觀察的一個完全不同的設計模塊。然后工程師利用有源探頭特點強制賦予不同的數(shù)值,確保電路適當響應的方式,進一步改善了設計。

對FPGA設計人員來說,增強調試能力是影響重大。最新的解決方案能夠顯著縮短調試驗證時間,為FPGA提供無與倫比的可觀察性和可控性。結果使得,在選擇器件時更重視FPGA調試能力的設計人員,可以縮短開發(fā)周期,降低成本,同時顯著加快上市速度。